A 8-month program covering Scan, ATPG, JTAG, and MBIST with hands-on projects using Mentor Graphics Tessent and Synopsys TetraMax tools. Learn the complete DFT flow from RTL to gate-level implementation.

Next Batch

1-1 Dedicated Mentor Support

24/7 Tool Access

Multiple Mock Interviews

Industry Standard Projects

Support with Resume Update

DFT Training Overview

Course Overview

DFT (Design for Testability) Training – Summary

Duration: 8 months comprehensive program

Tools:

- Synopsys TetraMax

- MentorGraphics Tessent (12 months tool access post-course with extension option).

Placement Support: Institute provides placement support till candidate gets a JOB

Training Highlights:

- DFT Fundamentals

- Fault models: Stuck-at, Transition Delay, and Path Delay

- SoC Scan Architecture and Types of Scan Designs

- ATPG DRC Debug and Simulation Debug

- JTAG, MBIST (Memory Built-In Self Test), and LogicBIST techniques

- Test Compression Techniques using TestKompress

- Hierarchical Scan Design and DFT Diagnosis

Hands-on Training:

- Work on a complex SoC design with multiple memory blocks

- Apply MemoryBIST to test embedded memories

- Boundary Scan used to manage MBIST controllers with fewer external pins

- ATPG Pattern Generation for multiple fault models

- Simulation-based validation of compressed test patterns

Assignments & Practice:

- Extensive assignments for ATPG, Scan insertion, compression and JTAG

- Multiple test cases and scenarios using Tessent tool

- Practical exercises aligned with current industry needs

Training Delivery:

- Concept-focused sessions with real-time lab practice

- Delivered by experienced trainers from the DFT domain

Program Highlights:

- In-depth, industry-relevant understanding of DFT methodologies

- Hands-on learning with advanced fault models and scan architecture

- Focus on ATPG, Scan, BIST, Compression, and Simulation Debug

- Institute Info:

- Offered by VLSIGuru, established in 2012

- Trained over 10,000+ students

- Affordable in-class training in Bangalore

- Online training available for students outside Bangalore

Detailed overview:

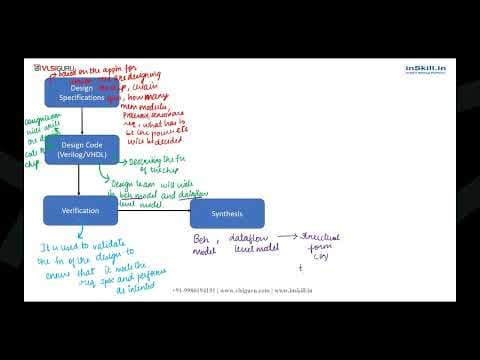

DFT(Design for Testability) involves using SCAN, ATPG, JTAG and BIST techniques to add testability to the Hardware design. These techniques are targeted for developing and applying tests to the manufactured hardware. There tests in turn help catch manufacturing defects like stuck at 0, 1 faults, and transition delay faults etc.

DFT Training will focus on all aspects of testability flow including DFT basics, various fault types, SOC Scan Architecture, different scan types, ATPG DRC Debug, ATPG Simulation debug, and DFT diagnosis. DFT Training course will also focus on JTAG, MemoryBIST, LogicBIST, Scan and ATPG, test compression techniques and Hierarchical scan design.

As part of DFT Training, a complex design example with variety of memories spread around the design used as a reference for learning all testability. While MBIST used to test memories. Boundary scan is a requirement for designs, used to control the MBIST controllers that are created to minimize the need for having extra external pins to run the memory tests. ATPG test patterns will be created for various different fault models like stuck-at, transition delay, path delay fault models. Various TestKompress techniques will be used to compress test patterns to ensure patterns can be applied on minimal number of IO pins used during test. Compressed test patterns will run more quickly on the production test floor and require less tester memory. Patterns are validated through Simulations.

DFT Training course is designed as per the current industry requirements with multiple hands on projects based on Scan, ATPG, JTAG and MBIST. DFT Training will help student with in-depth knowledge of all testability techniques. Hands-on project will involve creating large number of test cases for various aspects like Scan insertion, Compression, JTAG and ATPG pattern generation using Tessent tool. More importance is given to basic concepts, interaction sessions, hands-on, important notes and assignments.

MentorGraphics Tessent tool is used for training. As per industry survey, it is used by more than 80% companies for DFT. Student will have access to tool at the institute for 12 months after course completion, with a provision to extend beyond.

Mentor Graphics Tessent and Synopsys

Key Features

Who All Can Attend This DFT Training?

This training is ideal for professionals aiming to specialize in testability design techniques for VLSI and SoC development. It is suitable for both working engineers and fresh graduates looking to build careers in semiconductor testing and design.Pre-requisites To Take Design for Testability (DFT)

- There are no prerequisites for DFT training, however, having a basic understanding of Digital logic and VLSI design flow is an added advantage.

High Demand for Design for Testability (DFT)

Know about the Growing VLSI industry

DFT Engineers are highly valued in semiconductor companies for optimizing test coverage and reducing silicon defects. Salaries grow significantly with expertise in scan insertion, ATPG, MBIST, and experience using tools like Synopsys DFT Compiler and Tessent. Bangalore, Hyderabad, and Noida offer the highest compensation.

₹8 LPA

₹12 LPA

₹16 LPA

₹20 LPA

₹25 LPA

As semiconductor designs become more complex, the need for skilled DFT engineers continues to grow rapidly. Enrolling in a structured Design for Testability training program helps candidates understand how test logic is integrated into chip design to ensure quality and reliability.

A well-designed DFT engineer training for freshers focuses on scan insertion, ATPG, fault modeling, and test coverage techniques. For graduates entering the VLSI domain, a DFT course for freshers provides the right foundation to transition into test engineering roles with confidence.

Learn Through Real-Time Projects and Industry Practices

To succeed in DFT roles, practical exposure is essential. Programs offering DFT training with real time projects allow learners to work on real chip-level scenarios, improving their understanding of scan chains, fault simulation, and test pattern generation.

An advanced VLSI DFT training program integrates Industry Standard Projects, structured assignments, and hands-on tool usage. With real time DFT training with internship, candidates gain experience in real workflows followed in semiconductor companies.

Learners can choose between flexible online DFT training course options or enroll in an offline DFT training institute for classroom-based learning, depending on their preference.

Internship Programs That Enhance Job Readiness

One of the biggest advantages of enrolling in a professional program is access to structured internships. A DFT training and internship program provides candidates with real-time exposure to test engineering processes.

Programs offering a 6 months DFT training and internship or a training and internship for DFT engineer ensure deeper practical understanding. For fresh graduates, a DFT internship for freshers or a DFT internship with placement support significantly improves employability.

A well-structured DFT course with internship and placement ensures that candidates gain both technical knowledge and industry experience before entering the job market.

Designed for Engineering Graduates and Freshers

A comprehensive DFT training for engineering graduates is tailored to help candidates build strong fundamentals in testability concepts. Programs offering DFT training for ECE students and DFT training for EEE students ensure that learners from core electronics backgrounds can easily adapt to DFT roles.

A structured DFT engineer course for freshers focuses on industry-relevant tools and methodologies, making it easier for candidates to handle real-time challenges in semiconductor testing.

Placement-Focused Training for Career Growth

Choosing a DFT training with placement can significantly improve your career opportunities. Programs designed as a placement-oriented DFT course include resume building, technical interview preparation, and Mock Interviews to prepare candidates for hiring processes.

A DFT course with job assistance or DFT placement training ensures that learners are fully equipped to secure roles in semiconductor companies. Enrolling in a placement-focused DFT course or a design for testability course with placement aligns your skills with current industry demands.

Additionally, a DFT job support training program helps candidates even after course completion by providing guidance during job transitions.

Flexible Learning Options with Expert Support

Modern learners require flexibility, and a weekend DFT training or online DFT training course allows working professionals and students to upskill without disrupting their schedules.

A high-quality DFT training institute provides continuous Expert Faculty Support, regular doubt clarification sessions, and structured learning paths. Combined with hands-on practice and real-time exposure, this approach ensures consistent skill development.

Start Your Journey in DFT Engineering

With increasing demand for test engineers, enrolling in a DFT training after engineering is a strategic move for fresh graduates. If you are looking for the best DFT training institute, the right program can accelerate your career.

A comprehensive job-oriented DFT training course or job-oriented DFT course equips you with both technical expertise and practical experience, helping you confidently step into roles as a DFT engineer in the semiconductor industry.

Explore a wide range of VLSI and Embedded Systems courses to get industry-ready.

50+ industry oriented courses offered.

Explore a wide range of VLSI and Embedded Systems courses to get industry-ready.

50+ industry oriented courses offered.