New Batch Starts In a Week

AMBA Protocol training is focused on all the aspects of APB, AXI and AHB from scratch covering all the aspects from signals, timing diagram, all the features.

Next Batch

1-1 Dedicated Mentor Support

24/7 Tool Access

Multiple Mock Interviews

Industry Standard Projects

Support with Resume Update

AMBA Protocol Training Overview

Course Overview

AMBA Protocol training is structured to enable engineers gain perfection in AXI, AHB & APB protocols. Majority of designs are based on ARM architecture. All ARM architectures are based on AMBA protocols(AXI, AHB and APB), which makes it essential for every design & verification engineer to have detailed understanding of these protocols. SoC design debug and testbench component coding in most cases involves either AXI and/or AHB protocols, and also majority of interviews are focused on candidate familiarity with AXI or AHB protocol. All this makes it essential for every VLSI engineer to have good working knowledge of these protocols.

AMBA Protocol training course focuses on teaching protocol concepts, features, timing diagrams from basic to advanced for AXI4.0, AHB2.0 and APB. Course also focus on teaching protocol testbench development concepts. Student has flexibility to choose specific protocol as well.

On-chip protocols

Peripheral protocols

Importance of AMBA protocols for VLSI engineer?

APB protocol basics

Features

APB system architecture

Signal descriptions

APB transaction state diagram

AXI Protocol features

AMBA protocol overview

ARM processor - categories

AMBA Protocol basics

Comparison of APB, AHB and AXI protocols.

Correlating AXI with APB protocol

Features added in AXI on top of APB protocol

Introduction

SOC Architecture – Significance of AXI protocol

AXI architecture components

How five channels help AXI protocol?

Write & Read Channels

AXI Channel handshaking

Write Channel Signals – Address, Data and Response

Read Channel Signals – Address and Data

Ports added in AXI protocol

Write Transaction Timing Diagram

How to draw timing diagrams?

Read Transaction Timing Diagram

Big endian and little-endian architecture

Wrap write and read transactions

Narrow transfers

Data bus and strobe relation

Responses in AXI

Locked and exclusive transfers

Aligned and unaligned transfers

Overlapping, out of order, interleaved txs

Interconnect role in out of order transaction

Significance of ID in AXI protocol

AXI Channel handshake dependency

Cacheable and bufferable transactions

Protected transactions

New ports added

Memory attributes signalling

Modifiable transactions

Non-modifiable transactions

Read-allocate and write-allocate

Memory types

Transaction buffering

QoS signalling

Multiple region signalling

User-defined signalling

Need for UVC?

Different types of UVC's

Active

Master

Slave

Passive

UVC usage in module and SOC verification

Where Passive UVC are used?

UVC integration into TB

AXI UVC architecture

AXI Transaction Definition

AXI UVC component coding

Driver, sequencer, monitor, coverage

Environment, interface, slave model

Transaction, assertions

AXI UVC integration

AXI scoreboard coding

UVC integration in SOC TB

Testcase and sequence coding

Waveform analysis

Assertion coding and analysis

Functional coverage analysis

AHB and AXI: How they differ?

AHB based system architecture

AHB transfers: Various phases

Arbitration Phase

Address Phase

Data Phase

Burst transfers

Aligned transfers

Narrow transfers

Incrementing and wrapping transactions

Exclusive transfers

Exclusive access monitor

Exclusive Access signaling

Exclusive transfer restrictions

Resp signal

Two cycle response

Split and retry responses

UVC architecture

UVC components

UVC types

Master, slave

Active, Passive

UVC test case listing down

UVC component coding

Driver, sequencer, monitor, coverage

Environment, interface, slave model

Transaction, assertions

UVC Component integration

Sequence and test case development

Simulations, waveform analysis

Functional coverage analysis

Assertion coding and analysis

Key Features

Who All Can Attend This AMBA Protocol Training?

This training is ideal for professionals and graduates aiming to work on ARM-based SoC designs, with a focus on understanding and implementing AMBA protocols in VLSI design and verification flows. It is highly relevant for those involved in IP development, integration, and verification.Pre-requisites To Take AMBA (AXI, AHB, And APB) Protocol Training

- Exposure to any bus protocols like I2C, SPI, etc.

- Exposure to digital design concepts

High Demand for AMBA (AXI, AHB, And APB) Protocol Training

Know about the Growing VLSI industry

Verification engineers with strong protocol-level knowledge (especially AXI/AMBA) are highly valued in SoC and IP verification teams. Engineers skilled in UVM, SV, and protocol debugging typically work on high-speed interconnects and gain quicker access to lead or architect roles.

₹7 LPA

₹11 LPA

₹15 LPA

₹19 LPA

₹25 LPA

- Customized training programs for teams

- Upskill and reskill employees with industry-relevant content

- Interactive sessions led by expert trainers

- Hands-on projects and real-world case studies

- Flexible delivery in online

- Improve productivity and efficiency

- Access to training resources and material

- Learn in real-time with instructor-led sessions

- Flexible access from anywhere

- Recorded sessions available for revision

- Training on industry-standard tools

- Get certification after completion

- Self-paced learning as per your flexibility

- Industry-aligned learning modules

- Certification after course completion

- Access to structured video lessons and materials

- Track your progress step by step

- Access to learning materials for more than 1.5 years

AMBA Protocol Training is essential because AXI, AHB, and APB are the backbone of most ARM-based SoCs, prevalent in the VLSI industry. Mastering these protocols is crucial for effective design, verification, and debugging of complex integrated circuits. A strong understanding significantly enhances employability in VLSI roles, as most interviews heavily focus on AMBA protocol knowledge. This training equips engineers with the necessary skills for success in the core of modern VLSI design.

Career Path

Learning Path

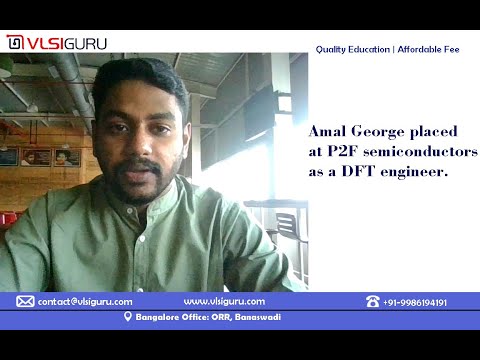

At VLSIGuru, we believe that education should lead to meaningful employment. Our training programs are designed not just to impart technical excellence, but also to bridge the gap between academic learning and industry demands. With a strong network of hiring partners and a proven track record, we ensure that our students are career-ready.

Placement Highlights

- Industry-aligned curriculum

- Hands-on projects and case studies

- Communication skills

- Resume building and interview preparation

- Technical and HR mock sessions

- Aptitude and domain-specific test series

- Regular drives and exclusive hiring events with partner companies

- Resume building and interview preparation

At VLSIGURU, we provide industry-focused VLSI training and guidance that helps students and professionals build strong technical skills and succeed in their careers. Our programs are designed to be practical, flexible, and aligned with current industry requirements.

Student Reviews

Frequently Asked Questions

- Course presentations for all topics

- Session notes

- Lab documents with detailed steps

- User guides

- Exposure to any bus protocols like I2C, SPI, etc.

- Exposure to digital design concepts

Yes. Participant will gain exposure to following aspects

- VIP development for AXI3 protocol

- UVC development for AHB2 protocol

- UVC development for APB protocol

- Analysing AXI, AHB and APB timing diagrams in simulations

- Functional coverage analysis

- Assertion coding and debugging

Each session of course is recorded, missed session videos will be shared

- Yes, You will have option to view the recorded videos of course for the sessions missed

- You will have option to repeat the course any time in next 1 year

- Yes, Course fee also includes support for doubt clarification sessions even after course completion

- You have option to mail you queries

- Option to meet in person to clarify doubts

- Sources and related content

Start by understanding the AHB specification, then learn Verilog for hardware description. VLSI Guru's course provides hands-on labs with clear steps to guide you from basics to implementation.

AHB is for high-performance, complex interconnects with pipelining, while APB is a simpler, low-bandwidth protocol for peripherals. VLSI Guru's course clarifies these distinctions with practical examples.

AMBA protocols, like AHB and AXI, are communication standards whose behavior is often described and implemented using Verilog. At VLSI Guru, you'll learn to model these protocols effectively in Verilog.

AMBA protocols standardize on-chip communication, enabling efficient integration and reuse of IP blocks, reducing design complexity and time-to-market – skills you'll master at VLSI Guru.

The three main types are: behavioral, dataflow, and structural. VLSI Guru's comprehensive approach ensures you're proficient in all modeling styles relevant to AMBA implementation.

The best way is through a structured course like VLSI Guru's, combining theoretical understanding with practical coding exercises and expert guidance.

AHB (Advanced High-performance Bus) is used for high-speed data transfers between masters like processors and memory within an SoC. VLSI Guru's course will equip you to design and verify AHB-based systems.

The arbiter grants exclusive access to the AHB bus to one master at a time, preventing collisions. Understanding arbitration is a key part of VLSI Guru's AHB module.

AMBA 2 (shared bus), AMBA 3 (point-to-point AXI), and AMBA 4 (coherency with ACE). VLSI Guru's curriculum systematically covers the evolution and features of each generation.

Advantages include IP reuse, reduced complexity, and improved performance through standardization – all crucial for efficient SoC development, which you'll learn at VLSI Guru.

AMBA stands for Advanced Microcontroller Bus Architecture, standardizing on-chip communication for efficient SoC design. VLSI Guru provides a deep dive into its architecture and applications.

Cache coherency ensures data consistency across multiple processors, vital for reliable parallel processing in advanced SoCs. VLSI Guru’s course explores these advanced concepts.

The arbiter manages bus access, ensuring only one master drives the bus at a time, preventing data corruption. VLSI Guru's hands-on labs demonstrate arbiter implementation and behavior.