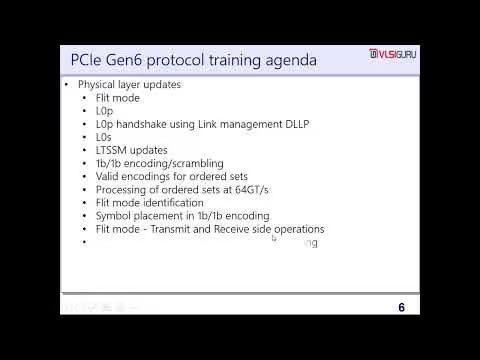

PCIe Gen6 training focused on Flit mode, PAM4 signaling, all the updates resulting from these features.

Next Batch

1-1 Dedicated Mentor Support

24/7 Tool Access

Multiple Mock Interviews

Industry Standard Projects

Support with Resume Update

PCIe Gen6 Training Overview

PCIe gen6 Training

A course on PCIe (Peripheral Component Interconnect Express) Gen6 is typically designed to provide in-depth knowledge about the latest generation of the PCIe standard, its architecture, features, and implementation. ers of PCIe.

- Introduction to PAM4 (Pulse Amplitude Modulation with 4 Levels).

- Advantages over NRZ for achieving 64 GT/s.

- Signal integrity challenges (noise, jitter, crosstalk).

- Receiver equalization for PAM4.

Key Features

Who All Can Attend This PCIe Gen6 Training?

This training is ideal for professionals looking to master high-speed serial protocols and gain hands-on experience with PCIe Gen6 architecture, design, and verification. It is suitable for both beginners and experienced engineers working in semiconductor and system design domains.Pre-requisites To Take PCIe Gen6 Training

- Exposure to standard bus protocols

- Exposure to Testbench component coding using SystemVerilog

High Demand for PCIe Gen6 Training

Know about the Growing VLSI industry

Responsible for developing verification plans, creating test benches, and executing tests to ensure the functionality and compliance of PCIe Gen6 interfaces in SoCs or IP.

In India, the demand for verification engineers specializing in high-speed protocols like PCIe is steadily growing with the expanding semiconductor design sector.

An estimated 20-25% of VLSI engineering roles in India focus on verification, with a rising need for PCIe expertise.

₹4 LPA

₹7 LPA

₹8 LPA

₹15 LPA

₹22 LPA

AI integrated learning for future VLSI engineers

Explore a wide range of VLSI and Embedded Systems courses to get industry-ready.

50+ industry oriented courses offered.

Explore a wide range of VLSI and Embedded Systems courses to get industry-ready.

50+ industry oriented courses offered.