System Verilog Course is a 9-week intensive course covering System Verilog constructs, advanced verification techniques, and 200+ industry examples with hands-on labs.

Next Batch

1-1 Dedicated Mentor Support

24/7 Tool Access

Multiple Mock Interviews

Industry Standard Projects

Support with Resume Update

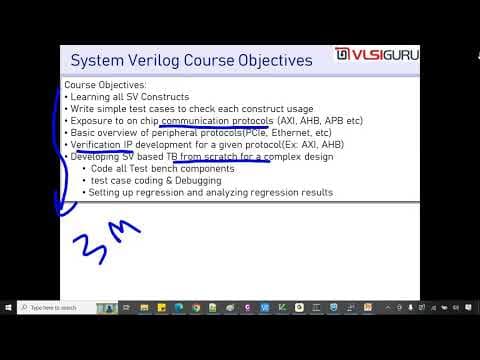

System Verilog Course Overview

Course Overview

System Verilog training is a 9 weeks course provides in-depth exposure to all the language constructs. Each and every session emphasizes on providing practical use cases for all constructs. Course includes 15+ assignments with dedicated lab sessions to support with the assignment completion.

System Verilog Training course is provides participants with exposure to advanced functional verification techniques including constrained random verification, assertion based verification, and coverage based verification. The course is targeted for engineers with all experience levels, starting from a BE, ME fresher to experienced engineers. System Verilog Training course is also targeted for engineers working in non-VLSI domains and planning to switch in to VLSI. Learning starts from basic examples to entire test bench development coding, to ensure a smooth learning curve.

System Verilog language in learnt using more than 200+ detailed examples covering all aspects of SV starting from data types, operators, OOPs(Classes), Arrays, Inter-process synchronization, Interface, Program, constraints and randomization, code coverage, functional coverage, DPI and assertions. These examples cover more than 90% of questions asked in VLSI interviews.

System Verilog Training course also involves 18 detailed assignments. These assignments are prepared by industry experts covering all aspects of SV from language constructs. Student gets to work on these assignments with complete guidance from trainers.

Functional Verification overview

- Test bench architecture

- Test bench components

- Test bench development : Modularity, Reusability

- Understanding Functional Verification flow

System Verilog Course overview

- System Verilog language features

- Verilog for TB development

- Verilog Language constructs and shortcomings

operators, data types

- Literals

- Operators – How things change from Verilog

- Data types

- Integer based

- string

Arrays

- Array classification

- Packed and Unpacked Arrays

- Static and Dynamic Arrays

- Multi dimensional Arrays

- Dynamic Arrays

- Associative Arrays

- Queue

- Array of Queues in scoreboard implementation, other complex declarations

Object Oriented Programming

- Basics of OOP

- Class, Object, handle

- Class elements

- Properties, methods, constraints

- Properties – 5 attributes in property declaration

- rand/randc, signed, static, 2/4 state, data hiding

- Language provided and User defined methods

- Developing Ethernet frame and APB Tx class

- new constructor

- randomize, pre_randomize, post_randomize

- User defined methods – print, copy, compare, pack, unpack

- Encapsulation – Data hiding, local, protected, public

- Inheritance

- Ethernet frame generation example to learn OOP

- Polymorphism – real life usecases

- this, super

- Class forward declaration

- Multiple levels of inheritance

- Abstract class

- Parameterized classes

- Difference from Verilog parameterization

- Parameterization with inheritance – 4 combinations

- Parameterized classes for testbench development

- Static properties and methods

- Interface class

- Constant class property

- Scope resolution operator

- Nested class

- Variable scope

- Object copying – copy by handle, shallow copy, deep copy

- $cast – static and dynamic casting

Advanced data types

- Data types

- Chandle, event, typedef, struct, union, enum

- Using struct data type for medals tally sorting example

- Typedef for defining complex data types

- Using complex data types in scoreboard development

Fork join, Inter process synchronization

- Labeling

- Fork join – join_any, join, join_none

- Nested fork

- Labeling fork

- Process, process states

- Inter process synchronization

- IPS constructs – mailbox, event, Semaphore

- mailbox – types, methods

- events – persistant, synchronization examples

- Semaphore – synchronization examples

Project to learn all SV language constructs

- Project – Memory TB development covering 90% of SV language constructs

- Configurable memory TB development

- Interface – Ports, internal signals, clocking block, modport

- using clocking block to fix design – TB synchronization issues

- Physical interface, virtual interface

- Using interface for design and TB connection

Program

- Program significance

- How Program differs from Module

- Why Program is redundant?

Scheduling semantics

- Scheduling semantics

Task, Function

- Task, function – how they are different from Verilog

- Static & automatic task/functions

- System task and functions

Constraints

- Constraints format

- Constraints type

- Simple

- distribution

- implication

- if-else

- iterative

- variable ordering

- soft

- unique

- Inline constraints

- Constraints for queue randomization

- Constraints virtual nature

Randomization

- Randomization in class, module

- rand, randc

- randcase

- Multiple hands on examples on Constraints and Randomization

- Chip select example using multiple inter related constraints

- new significance for randc

- Constrained random verification

- Directed verification

Functional coverage

- What is functional coverage?

- Need for functional coverage

- Where FC comes in functional verification flow?

- How to implement FC?

- Different types of FC?

- Integrating Functional coverage in Test bench

- functional coverage hierarchy

- Different types of coverpoints – simple, cross, transition

- Different types of bins – normal, illegal, ignore

- coverage calculation

- coverage options

- auto_bin_max

- weigth

- at_least

- goal

- comment

- name

- per_instance

- detect_overlap

- Listing down cover points for a design

- Instance coverage

- Cross coverage with intersect

- FC system task & Functions

- Coverage Driven Verification

- Coverage report analysis

- Cover groups with arguments

- Coverage filter using iff

- Functional coverage types in TB

- transaction class coverage

- register field coverage

- scenario coverage

Code coverage

- Generating code coverage

- Different types – FCBEST

- FSM

- Conditional

- Branch

- Expression

- Statement

- Toggle

- Detailed understanding of code coverage types with examples

Coverage report analysis

- Merging UCDBs, generating coverage reports

- Analyzing coverage report

- Coverage exclusion

Assertions and Assertion based verification

- Need for assertions?

- Assertion based verification

- Types of assertions

- Immediate assertions

- Concurrent assertions

- Assertion format – antecedent, consequent

- Running assertions using questasim, debugging the assertions in waveform

- Assertion hierarchy – property, sequence, boolean expression

- ##, |-> and |=> operators

- Assertion examples for clock frequency check

- Assertion with local variables

- Assertions for simple timing diagrams

- Listing down and implementing assertions for simple designs

- Async FIFO

- Interrupt controller

DPI

- Direct Programming Interface(DPI)

- import and export of functions

Configuration libraries, Packages, XMR

- Configuration Libraries

- Incremental compilation

- Packages – defining, importing

- XMR

Remaining SV topics

- Compiler directives

- Macros

- Parameterizable macros

- VCD – value change dump

- common array methods

- Callbacks – multiple use case examples

Key Features

Who All Can Attend This System Verilog Course?

This System Verilog course welcomes BE/ME freshers and experienced engineers aiming to master advanced verification techniques for VLSI or transitioning from non-VLSI domains.Pre-requisites To Take System Verilog Course

- Verilog & Digital Design

- Exposure to coding design & testbench using Verilog (Ex: FIFO design & verification using Verilog)

High Demand for System Verilog Course

Know about the Growing VLSI industry

Responsible for creating UVM-based testbenches, developing verification plans, writing test cases, and ensuring that the RTL design meets all functional requirements.

Over 70% of semiconductor companies require UVM skills for verification roles.

UVM-trained verification engineers are 40% more likely to be hired for high-budget projects.

Verification roles contribute to 60% of hiring demand in front-end VLSI design teams.

₹6 LPA

₹9 LPA

₹14 LPA

₹20 LPA

₹28 LPA

AI integrated learning for future VLSI engineers

Explore a wide range of VLSI and Embedded Systems courses to get industry-ready.

50+ industry oriented courses offered.

Explore a wide range of VLSI and Embedded Systems courses to get industry-ready.

50+ industry oriented courses offered.